- VLSI Design Tutorial

- VLSI Design - Home

- VLSI Design - Digital System

- VLSI Design - FPGA Technology

- VLSI Design - MOS Transistor

- VLSI Design - MOS Inverter

- Combinational MOS Logic Circuits

- Sequential MOS Logic Circuits

- VHDL Programming

- VHDL - Introduction

- VHDL - Combinational Circuits

- VHDL - Sequential Circuits

- VLSI Design Useful Resources

- VLSI Design - Quick Guide

- VLSI Design - Useful Resources

- VLSI Design - Discussion

VLSI 设计 - 快速指南

VLSI 设计 - 数字系统

超大规模集成 (VLSI) 是通过将数千个晶体管组合到单个芯片中来创建集成电路(IC) 的过程。VLSI 始于 20 世纪 70 年代,当时正在开发复杂的半导体和通信技术。微处理器是VLSI器件。

在引入 VLSI 技术之前,大多数 IC 只能执行有限的功能。电子电路可能由CPU、ROM、RAM和其他胶合逻辑组成。VLSI 允许 IC 设计人员将所有这些功能添加到一个芯片中。

电子行业在过去几十年中取得了惊人的增长,这主要归功于大规模集成技术和系统设计应用的快速发展。随着超大规模集成(VLSI)设计的出现,集成电路(IC)在高性能计算、控制、电信、图像和视频处理以及消费电子领域的应用数量一直在快速增长。

当前的尖端技术,如高分辨率、低比特率视频和蜂窝通信,为最终用户提供了大量的应用、处理能力和便携性。这一趋势预计将迅速增长,对超大规模集成电路设计和系统设计具有非常重要的影响。

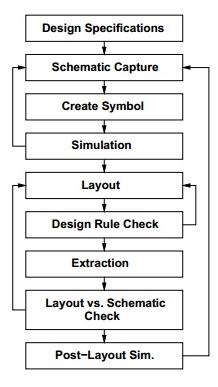

超大规模集成电路设计流程

VLSI IC电路设计流程如下图所示。设计的各个级别都进行了编号,并且块显示了设计流程中的过程。

规格是第一位的,它们抽象地描述了要设计的数字 IC 电路的功能、接口和架构。

然后创建Behave描述,以根据功能、性能、对给定标准的符合性和其他规范来分析设计。

RTL 描述是使用 HDL 完成的。该 RTL 描述经过模拟以测试功能。从这里开始我们就需要EDA工具的帮助了。

然后使用逻辑综合工具将 RTL 描述转换为门级网表。门级网表是根据门及其之间的连接对电路进行的描述,其制作方式满足时序、功率和面积规范。

最后,制作物理布局,对其进行验证,然后发送到制造。

Y图表

Gajski-Kuhn Y 图是一个模型,它捕捉了设计半导体器件时的考虑因素。

Gajski-Kuhn Y 图的三个域位于径向轴上。每个域都可以使用同心环分为多个抽象级别。

在顶层(外环),我们考虑芯片的架构;在较低级别(内环),我们不断将设计细化为更精细的详细实现 -

从Behave描述创建结构描述是通过高级综合或逻辑综合的过程来实现的。

从结构描述创建物理描述是通过布局合成实现的。

设计层次-结构

设计层次涉及“分而治之”的原则。无非是把任务分成更小的任务,直到达到最简单的水平。这个过程是最合适的,因为设计的最后演变已经变得如此简单,以至于其制造变得更加容易。

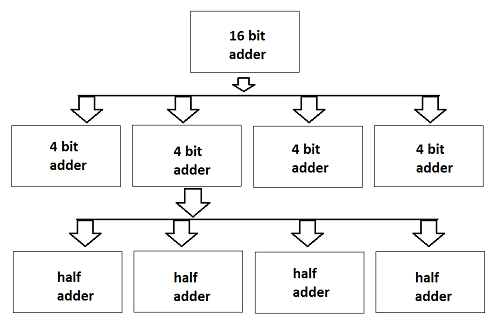

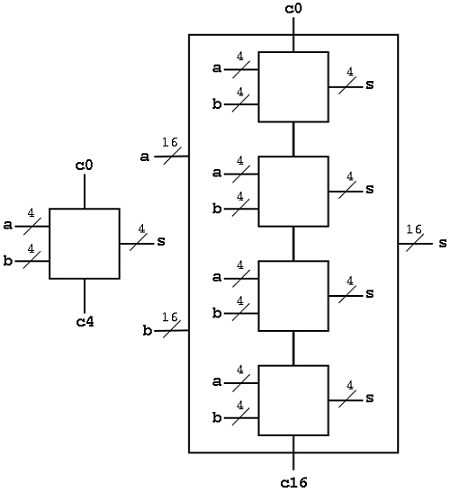

我们可以将给定的任务设计到设计流程的域(Behave、结构和几何)中。为了理解这一点,我们以设计一个16位加法器为例,如下图所示。

这里,整个16位加法器芯片被分为四个4位加法器模块。进一步地,将4位加法器分为1位加法器或半加器。1位加法是最简单的设计过程,其内部电路也很容易在芯片上制作。现在,连接所有最后四个加法器,我们可以设计一个 4 位加法器,继续,我们可以设计一个 16 位加法器。

VLSI 设计 - FPGA 技术

FPGA – 简介

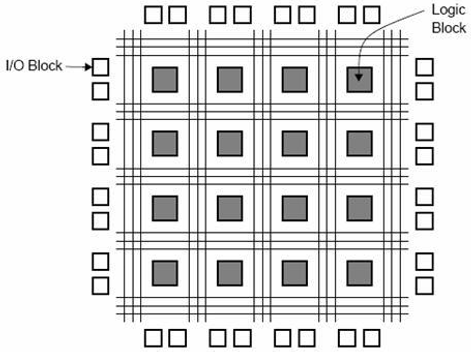

FPGA的完整形式是“现场可编程门阵列”。它包含一万到超过一百万个具有可编程互连的逻辑门。可编程互连可供用户或设计人员轻松执行给定的功能。典型的FPGA芯片模型如图所示。有I/O块,它们是根据功能设计和编号的。对于逻辑级组成的每个模块,都有CLB(可配置逻辑块)。

CLB 执行赋予模块的逻辑运算。CLB和I/O块之间的互连是借助水平布线通道、垂直布线通道和PSM(可编程多路复用器)来实现的。

它所包含的CLB数量只决定了FPGA的复杂程度。CLB 和 PSM 的功能由 VHDL 或任何其他硬件描述语言设计。编程后,CLB和PSM被放置在芯片上,并通过布线通道相互连接。

优点

- 需要的时间非常短;从设计流程到功能芯片。

- 其中不涉及物理制造步骤。

- 唯一的缺点是,它比其他款式贵。

门阵列设计

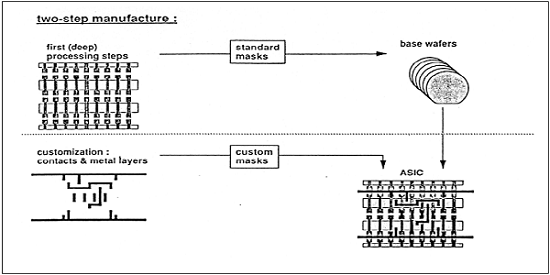

就快速原型设计能力而言,门阵列 (GA)位居第二,仅次于 FPGA。虽然用户编程对于 FPGA 芯片的设计实现很重要,但金属掩模设计和处理用于 GA。门阵列的实现需要两步制造过程。

第一阶段的结果是每个 GA 芯片上都有一组未使用的晶体管。这些未提交的芯片可以存储起来以供以后定制,这是通过定义阵列晶体管之间的金属互连来完成的。金属互连的图案化是在芯片制造过程的最后完成的,因此周转时间仍然很短,为几天到几周。下图显示了门阵列实现的基本处理步骤。

典型的门阵列平台使用称为通道的专用区域,用于 MOS 晶体管的行或列之间的单元间布线。它们简化了互连。执行基本逻辑门的互连模式存储在库中,然后可以使用该库根据网表自定义未提交的晶体管行。

在大多数现代 GA 中,多个金属层用于通道布线。通过使用多个互连层,可以在有源单元区域上实现布线;这样就可以像门海 (SOG) 芯片一样去除布线通道。这里,整个芯片表面都覆盖着未使用的 nMOS 和 pMOS 晶体管。可以使用金属掩模定制相邻晶体管以形成基本逻辑门。

对于单元间布线,必须牺牲一些未使用的晶体管。这种设计风格使互连更加灵活,并且通常具有更高的密度。GA 芯片利用率是用已用芯片面积除以总芯片面积来衡量的。它比FPGA更高,芯片速度也更高。

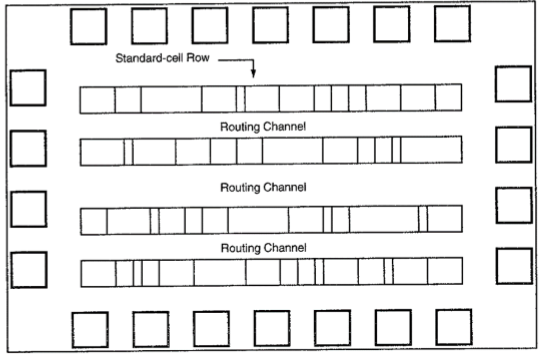

基于标准单元的设计

基于标准单元的设计需要开发完整的定制掩模组。标准电池也称为多电池。在这种方法中,所有常用的逻辑单元都被开发、表征并存储在标准单元库中。

一个库可能包含数百个单元,包括反相器、NAND 门、NOR 门、复杂 AOI、OAI 门、D 锁存器和触发器。每种门类型都可以实现多个版本,以便为不同的扇出提供足够的驱动能力。反相器门可以有标准尺寸、双倍尺寸和四倍尺寸,以便芯片设计者可以选择合适的尺寸以获得高电路速度和布局密度。

每个细胞根据几个不同的表征类别进行表征,例如,

- 延迟时间与负载电容

- 电路仿真模型

- 时序仿真模型

- 故障模拟模型

- 用于布局布线的单元数据

- 掩模数据

为了自动放置单元和布线,每个单元布局都设计有固定的高度,以便多个单元可以并排形成行。电源轨和接地轨与电池的上边界和下边界平行。因此,相邻单元共享公共电源总线和公共接地总线。下图是基于标准单元设计的平面图。

全定制设计

在全定制设计中,整个掩模设计都是全新的,无需使用任何库。这种设计风格的开发成本正在上升。因此,设计重用的概念逐渐流行起来,以减少设计周期时间和开发成本。

最难的全定制设计可能是存储单元的设计,无论是静态的还是动态的。对于逻辑芯片设计,在同一芯片上使用不同设计风格(即标准单元、数据路径单元和可编程逻辑阵列(PLA))的组合可以获得良好的协商。

实际上,设计人员进行完整的定制布局,即每个晶体管的几何形状、方向和布局。设计生产率通常很低;每个设计师通常每天需要几十个晶体管。在数字CMOS VLSI中,由于人工成本较高,几乎不采用全定制设计。这些设计风格包括存储芯片、高性能微处理器和FPGA等大批量产品的设计。

VLSI 设计 - MOS 晶体管

互补 MOSFET (CMOS) 技术如今被广泛用于在众多不同的应用中形成电路。当今的计算机、CPU 和手机都使用 CMOS,因为它有几个关键优势。CMOS 在两种状态下都具有低功耗、相对较高的速度和高噪声容限,并且可在较宽的源电压和输入电压范围内运行(假设源电压固定)

对于我们将讨论的工艺,可用的晶体管类型是金属氧化物半导体场效应晶体管 (MOSFET)。这些晶体管形成为“三明治”,由半导体层组成,通常是硅单晶的切片或晶片;一层二氧化硅(氧化物)和一层金属。

MOSFET的结构

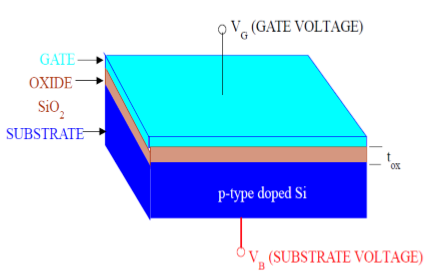

如图所示,MOS结构包含三层 -

金属栅电极

绝缘氧化层 (SiO 2 )

P型半导体(基板)

MOS结构形成一个电容器,栅极和衬底作为两块极板,氧化层作为介电材料。介电材料(SiO 2 )的厚度通常在10nm至50nm之间。衬底内的载流子浓度和分布可以通过施加到栅极和衬底端子的外部电压来控制。现在,要了解MOS的结构,首先要考虑P型半导体衬底的基本电特性。

半导体材料中载流子的浓度始终遵循质量作用定律。群体行动法由下式给出 -

$$np=n_{i}^{2}$$

在哪里,

n是电子的载流子浓度

p是空穴的载流子浓度

n i是硅的本征载流子浓度

现在假设衬底同样掺杂有浓度 N A的受主(硼) 。因此,p型衬底中的电子和空穴浓度为

$$n_{po}=\frac{n_{i}^{2}}{N_{A}}$$

$$p_{po}=N_{A}$$

这里,掺杂浓度N A比本征浓度ni大(10 15~10 16 cm -3 )。现在,为了理解 MOS 结构,请考虑 p 型硅衬底的能级图。

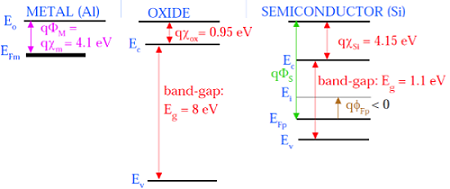

如图所示,导带和价带之间的带隙为1.1eV。这里,费米势 Φ F是本征费米能级 (E i ) 和费米能级 (E FP )之间的差值。

其中费米能级 E F取决于掺杂浓度。费米势 Φ F是本征费米能级 (E i ) 和费米能级 (E FP )之间的差值。

从数学上来说,

$$\Phi_{Fp}=\frac{E_{F}-E_{i}}{q}$$

导带和自由空间之间的电势差称为电子亲和势,用 qx 表示。

因此,电子从费米能级移动到自由空间所需的能量称为功函数 (qΦ S ),由下式给出

$$q\Phi _{s}=(E_{c}-E_{F})+qx$$

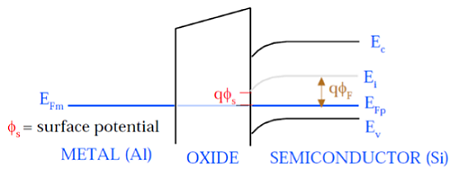

下图是组成MOS的元件的能带图。

如上图所示,绝缘SiO 2层具有8eV的大能带隙,功函数为0.95 eV。金属栅极的功函数为4.1eV。这里,功函数不同,因此会在 MOS 系统上产生压降。下图为MOS系统的组合能带图。

如图所示,金属栅极和半导体(Si)的费米电势水平处于相同电势。表面的费米势称为表面势 Φ S,其大小小于费米势 Φ F 。

MOSFET 的工作原理

MOSFET 由一个 MOS 电容器和两个靠近沟道区域的 pn 结组成,该区域由栅极电压控制。为了使pn结反向偏置,衬底电位保持低于其他三个端子电位。

如果栅极电压升高到超过阈值电压(V GS >V TO),表面就会形成反型层,源极和漏极之间就会形成n型沟道。该n型通道将根据V DS值承载漏极电流。

对于不同的 V DS值,MOSFET 可以工作在不同的区域,如下所述。

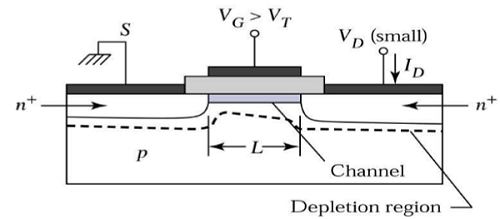

线性区域

当 V DS = 0 时,反向沟道区存在热平衡,漏极电流 I D = 0。现在,如果施加小漏极电压,V DS > 0,则与 V DS成比例的漏极电流将开始从源极流向通过通道排出。

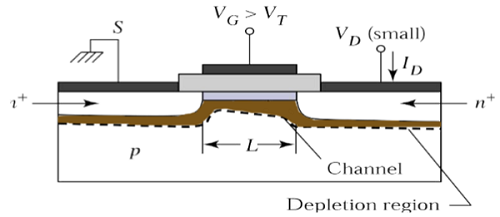

该沟道为电流从源极到漏极的流动提供了连续的路径。这种操作模式称为线性区域。工作在线性区的 n 沟道 MOSFET 的横截面图如下图所示。

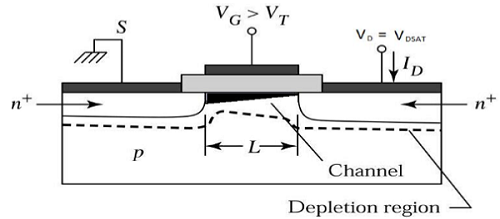

处于饱和区边缘

现在,如果 V DS增加,沟道中的电荷和沟道深度在漏极末端会减少。当V DS = V DSAT时,沟道中的电荷减少至零,这称为夹断点。工作在饱和区边缘的n沟道MOSFET的横截面图如下图所示。

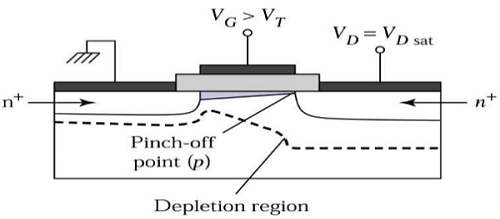

饱和区

当V DS >V DSAT时,在漏极附近形成耗尽表面,并且通过增加漏极电压,该耗尽区域延伸至源极。

这种工作模式称为饱和区。电子从源极到达沟道端,进入漏极耗尽区,并在高电场中向漏极加速。

MOSFET 电流-电压特性

为了了解 MOSFET 的电流-电压特性,需要对通道进行近似。如果没有这种近似,MOS 系统的三维分析就会变得复杂。电流-电压特性的渐进通道近似(GCA)将减少分析问题。

渐进通道逼近 (GCA)

考虑在线性模式下工作的 n 沟道 MOSFET 的横截面图。这里,源极和基板接地。V S = V B = 0。栅极至源极电压 (V GS ) 和漏极至源极电压 (V DS ) 电压是控制漏极电流 I D的外部参数。

将电压V GS设置为大于阈值电压V TO的电压,以在源极和漏极之间创建沟道。如图所示,x方向垂直于表面,y方向平行于表面。

这里,如图所示,源端 y = 0。相对于源极的沟道电压由V C(Y)表示。假设阈值电压 VTO 在 y = 0 到 y = L 之间沿沟道区域恒定。沟道电压 V C的边界条件为 -

$$V_{c}\left ( y = 0 \right ) = V_{s} = 0 \,and\,V_{c}\left ( y = L \right ) = V_{DS}$$

我们还可以假设

$$V_{GS}\geq V_{TO}$$和

$$V_{GD} = V_{GS}-V_{DS}\geq V_{TO}$$

令 Q1(y) 为表面反型层中的总移动电子电荷。该电子电荷可以表示为 -

$$Q1(y)=-C_{ox}.[V_{GS}-V_{C(Y)}-V_{TO}]$$

下图显示了地表逆温层的空间几何形状并指出了其尺寸。当我们从漏极移动到源极时,反演层逐渐减小。现在,如果我们考虑沟道长度 L 的小区域 dy,则该区域提供的增量电阻 dR 可以表示为 -

$$dR=-\frac{dy}{w.\mu _{n}.Q1(y)}$$

这里,负号是由于反型层电荷Q1的负极性而引起的,μ n是表面迁移率,其是恒定的。现在,将 Q1(y) 的值代入 dR 方程 -

$$dR=-\frac{dy}{w.\mu _{n}.\left \{ -C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} \右\}}$$

$$dR=\frac{dy}{w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} }$$

现在小 dy 区域的电压降可以由下式给出

$$dV_{c}=I_{D}.dR$$

将dR的值代入上式

$$dV_{C}=I_{D}.\frac{dy}{w.\mu_{n}.C_{ox}\left [ V_{GS}-V_{C(Y)} \right ]-V_ {致}}$$

$$w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C(Y)}-V_{TO} \right ].dV_{C}=I_{D}.dy $$

为了获得整个沟道区域的漏极电流 ID,可以沿沟道从 y = 0 到 y = L 以及电压 V C(y) = 0 到 V C(y) = V DS对上述方程进行积分,

$$C_{ox}.w.\mu _{n}.\int_{V_{c}=0}^{V_{DS}} \left [ V_{GS}-V_{C\left ( Y \right )}-V_{TO} \right ].dV_{C} = \int_{Y=0}^{L}I_{D}.dy$$

$$\frac{C_{ox}.w.\mu _{n}}{2}\left ( 2\left [ V_{GS}-V_{TO} \right ] V_{DS}-V_{DS} ^{2}\right ) = I_{D}\left [ L-0 \right ]$$

$$I_{D} = \frac{C_{ox}.\mu _{n}}{2}.\frac{w}{L}\left ( 2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2} \right )$$

对于线性区域 V DS < V GS – V TO。对于饱和区,V DS的值大于(V GS -V TO )。因此,对于饱和区,V DS = (V GS – V TO )。

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ 2V_{DS} \right ]V_{DS}-V_{ DS}^{2}}{L} \右)$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{2V_{DS}^{2}-V_{DS}^{2} {L} \右)$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ V_{GS}-V_{TO} \right ]^{ 2}}{L} \右)$$

VLSI 设计 - MOS 逆变器

逆变器确实是所有数字设计的核心。一旦清楚地了解了其操作和属性,设计更复杂的结构(例如与非门、加法器、乘法器和微处理器)就会大大简化。这些复杂电路的电气Behave几乎可以完全通过推断逆变器获得的结果来推导。

反相器的分析可以扩展到解释更复杂的门(例如 NAND、NOR 或 XOR)的Behave,这些门又构成乘法器和处理器等模块的构建块。在本章中,我们重点关注反相器门的一个具体化身,即静态 CMOS 反相器,或者简称 CMOS 反相器。这无疑是目前最受欢迎的,因此值得我们特别关注。

工作原理

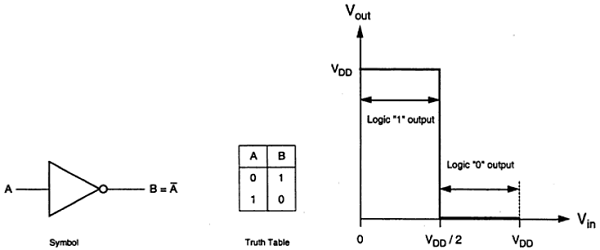

理想逆变器的逻辑符号和真值表如下图所示。这里 A 是输入,B 是由它们的节点电压表示的反相输出。采用正逻辑时,逻辑1的布尔值用V dd表示,逻辑0用0表示。V th是逆变器阈值电压,即V dd /2,其中V dd是输出电压。

当输入小于 V th时,输出从 0 切换至 V dd。因此,对于 0<V in <V th输出等于逻辑 0 输入,V th <V in < V dd等于反相器的逻辑 1 输入。

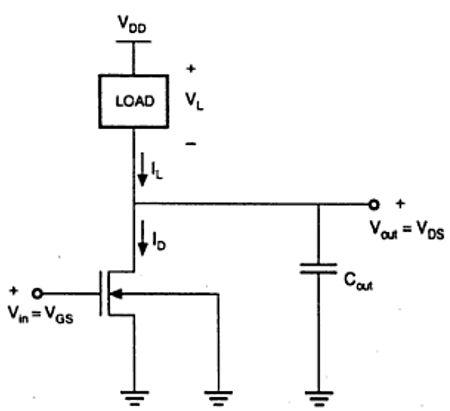

图中所示的特性是理想的。nMOS反相器的一般电路结构如下图所示。

从图中我们可以看出,反相器的输入电压等于nMOS晶体管的栅源电压,反相器的输出电压等于nMOS晶体管的漏源电压。nMOS的源极到衬底的电压也称为晶体管的驱动器,接地;因此V SS = 0。输出节点与用于VTC 的集总电容连接。

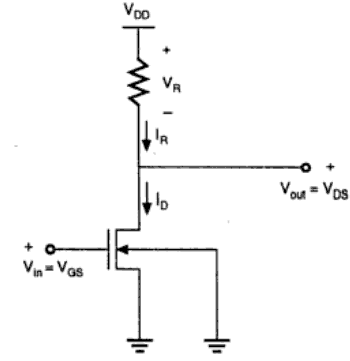

阻性负载逆变器

阻性负载逆变器的基本结构如下图所示。这里,增强型nMOS充当驱动晶体管。负载由一个简单的线性电阻器 R L组成。电路的电源为V DD,漏极电流I D等于负载电流I R。

电路操作

当驱动晶体管的输入低于阈值电压V TH (V in < V TH )时,驱动晶体管处于截止区域并且不传导任何电流。因此,负载电阻两端的压降为零,输出电压等于VDD。现在,当输入电压进一步增加时,驱动晶体管将开始传导非零电流,nMOS 进入饱和区。

从数学上来说,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

进一步提高输入电压,驱动晶体管将进入线性区,驱动晶体管的输出减小。

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

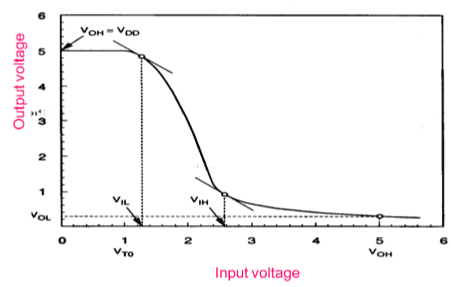

阻性负载逆变器的VTC如下图所示,表示驱动晶体管的工作模式和电压点。

N型MOSFET负载逆变器

使用MOSFET作为负载器件的主要优点是晶体管占用的硅面积小于电阻负载占用的面积。这里,MOSFET是有源负载,有源负载逆变器比阻性负载逆变器具有更好的性能。

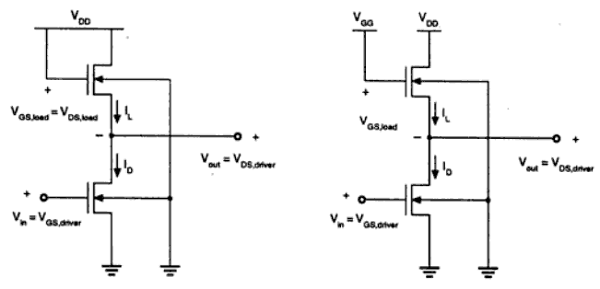

增强负载NMOS

图中所示为两台带有增强型负载装置的逆变器。负载晶体管可以在饱和区或线性区工作,具体取决于施加到其栅极端子的偏置电压。饱和增强型负载逆变器如图2所示。(A)。它需要单一电压源和简单的制造工艺,因此V OH被限制为V DD - V T。

线性增强型负载逆变器如图2所示。(二)。始终工作在线性区;因此V OH电平等于V DD。

与饱和增强型逆变器相比,线性负载逆变器具有更高的噪声容限。但是,线性增强型逆变器的缺点是,它需要两个独立的电源,并且两个电路的功耗都很高。因此,增强型逆变器并未用于任何大规模数字应用。

耗尽型负载 NMOS

增强型负载逆变器的缺点可以通过使用耗尽型负载逆变器来克服。与增强型负载逆变器相比,耗尽型负载逆变器需要更多的制造步骤来进行沟道注入来调整负载的阈值电压。

耗尽型负载逆变器的优点是——尖锐的VTC转换、更好的噪声容限、单电源和更小的总体布局面积。

如图所示,负载的栅极和源极端连接;因此,V GS = 0。因此,负载的阈值电压为负。因此,

$$V_{GS,load}> V_{T,load}$$ 满足

因此,无论输入和输出电压电平如何,负载设备始终具有传导通道。

当负载晶体管处于饱和区时,负载电流由下式给出

$$I_{D,负载} = \frac{K_{n,负载}}{2}\left [ -V_{T,负载}\left ( V_{out} \right ) \right ]^{2}$ $

当负载晶体管处于线性区时,负载电流由下式给出

$$I_{D,负载} = \frac{K_{n,负载}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \右]$$

耗尽负载逆变器的电压传输特性如下图所示 -

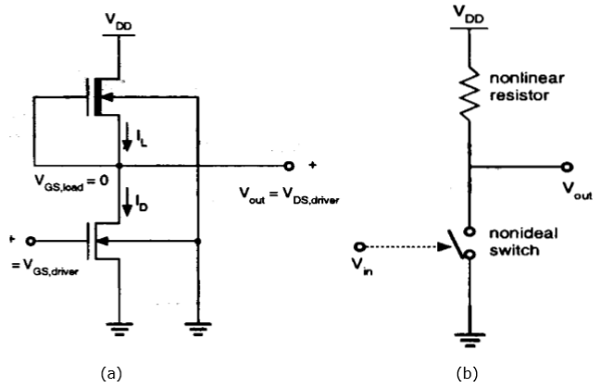

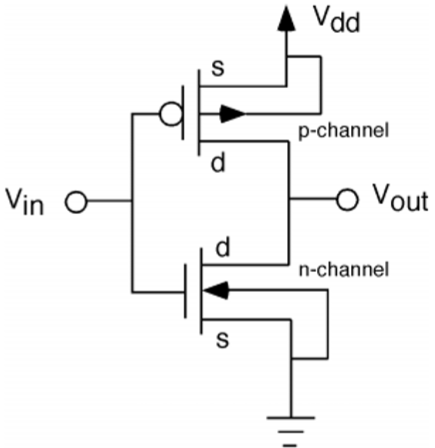

CMOS 逆变器 – 电路、操作和说明

CMOS反相器电路如图所示。这里,nMOS和pMOS晶体管用作驱动晶体管;当一个晶体管导通时,另一个晶体管截止。

这种配置称为互补 MOS (CMOS)。输入连接到两个晶体管的栅极端子,以便两个晶体管都可以直接用输入电压驱动。nMOS 的衬底接地,pMOS 的衬底连接到电源V DD。

因此两个晶体管的V SB = 0。

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{输出}$$

和,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

当nMOS的输入小于阈值电压(V in < V TO,n )时,nMOS截止,pMOS处于线性区。因此,两个晶体管的漏极电流均为零。

$$I_{D,n}=I_{D,p}=0$$

因此,输出电压V OH等于电源电压。

$$V_{输出}=V_{OH}=V_{DD}$$

当输入电压大于V DD + V TO,p时,pMOS 管处于截止区,nMOS 管处于线性区,因此两个管的漏极电流均为零。

$$I_{D,n}=I_{D,p}=0$$

因此,输出电压V OL为零。

$$V_{输出}=V_{OL}=0$$

如果 V in > V TO并且满足以下条件,则nMOS 工作在饱和区。

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{输出}\geq V_{输入}-V_{TO,n} $$

如果 V in < V DD + V TO,p并且满足以下条件,则pMOS 工作在饱和区。

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{输出}\leq V_{输入}-V_{TO,p} $$

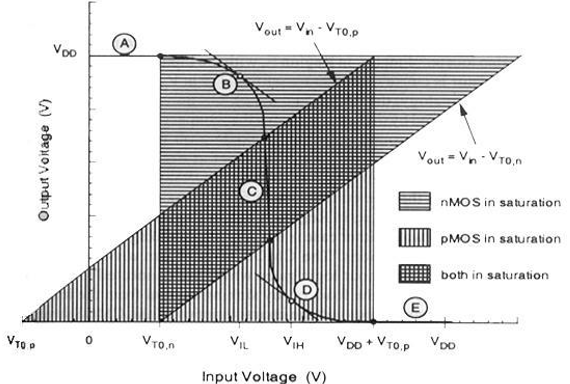

对于不同的输入电压值,下面列出了两个晶体管的工作区域。

| 地区 | 输入电压 | 输出电压 | nMOS | pMOS |

|---|---|---|---|---|

| A | < V TO, n | 电压_ | 隔断 | 线性 |

| 乙 | 电压_ | 高 ≈ V OH | 饱和 | 线性 |

| C | 电压_ | 电压_ | 饱和 | 饱和 |

| D | 电压_ | 低 ≈ V OL | 线性 | 饱和 |

| 乙 | > (V DD + V TO, p ) | 音量_ | 线性 | 隔断 |

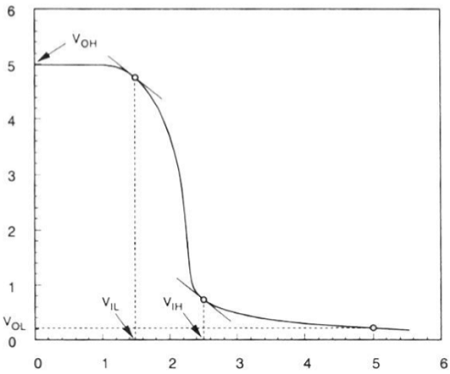

CMOS的VTC如下图所示 -

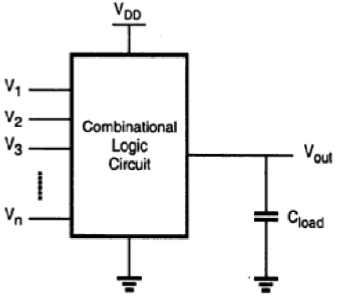

组合MOS逻辑电路

组合逻辑电路或门对多个输入变量执行布尔运算并将输出确定为输入的布尔函数,是所有数字系统的基本构建块。我们将研究简单的电路配置,例如双输入 NAND 和 NOR 门,然后将我们的分析扩展到多输入电路结构的更一般情况。

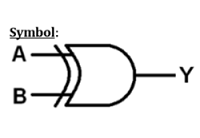

接下来,将以类似的方式呈现 CMOS 逻辑电路。我们将重点介绍nMOS耗尽型负载逻辑和CMOS逻辑电路的异同,并举例说明CMOS门的优点。在最一般的形式中,执行布尔函数的组合逻辑电路或门可以表示为多输入、单输出系统,如图所示。

以地电位为参考的节点电压代表所有输入变量。使用正逻辑约定,布尔(或逻辑)值“1”可以用 VDD 高电压来表示,布尔(或逻辑)值“0”可以用低电压 0 来表示。输出节点负载有电容CL ,它代表电路中寄生器件的组合电容。

CMOS逻辑电路

CMOS 二输入或非门

该电路由并联的n网和串联的互补p网组成。输入电压V X和V Y被施加到一个nMOS晶体管和一个pMOS晶体管的栅极。

当一个或两个输入都为高电平时,即当 n 网在输出节点和地之间创建导电路径时,p 网被切断。如果两个输入电压都很低,即n-net被截止,则p-net在输出节点和电源电压之间创建导电路径。

对于任何给定的输入组合,互补电路结构使得输出通过低电阻路径连接到V DD或接地,并且对于任何输入组合不建立V DD和地之间的DC电流路径。CMOS的输出电压,两个输入或非门将得到逻辑低电压V OL = 0和逻辑高电压V OH = VDD。开关阈值电压 V th的方程由下式给出

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\左 ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n }}}}$$

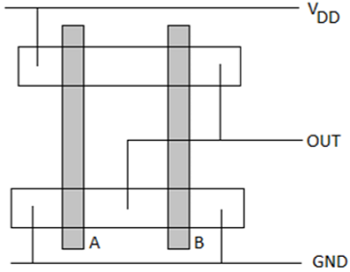

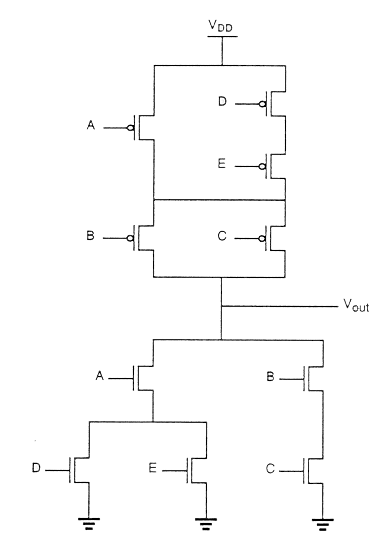

CMOS 2 输入或非门布局

该图显示了使用单层金属和单层多晶硅的 CMOS 2 输入 NOR 门的示例布局。这种布局的特点是 -

- 每个输入有一条垂直折线

- 分别用于 N 和 P 器件的单一活性形状

- 水平运行的金属巴士

CMOS N0R2门的棒图如下图所示;它直接对应于布局,但不包含W和L信息。扩散区域用矩形表示,金属连接以及实线和圆圈分别表示接触,交叉阴影条表示多晶硅柱。棒图对于规划最佳布局拓扑很有用。

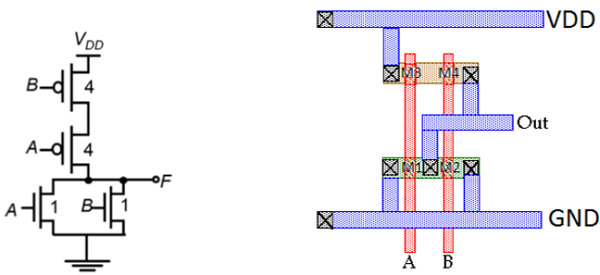

CMOS 二输入与非门

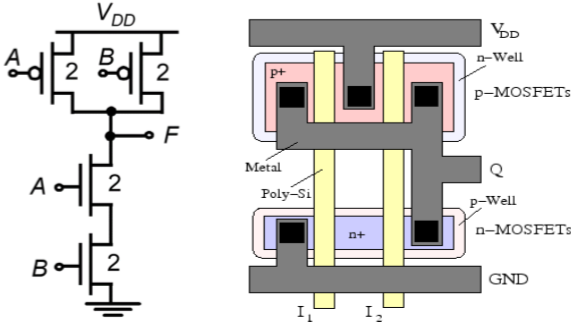

下图给出了两输入CMOS与非门的电路图。

该电路的工作原理正是CMOS双输入NOR运算。如果两个输入电压均为逻辑高电平,则由两个串联连接的 nMOS 晶体管组成的 n 网络会在输出节点和接地之间创建一条传导路径。p-net 中并联的两个 pMOS 晶体管都将截止。

对于所有其他输入组合,其中一个或两个 pMOS 晶体管将导通,而 p-net 被切断,从而在输出节点和电源电压之间创建一条电流路径。该门的开关阈值计算如下:

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}- \left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

这种布局的特点如下:

- 用于输入的单多晶硅线垂直穿过 N 和 P 有源区域。

- 单个有源形状用于构建 nMOS 器件和 pMOS 器件。

- 电源总线在布局的顶部和底部水平延伸。

- 输出线水平布置,以便于连接到相邻电路。

复杂逻辑电路

NMOS 耗尽负载复合逻辑门

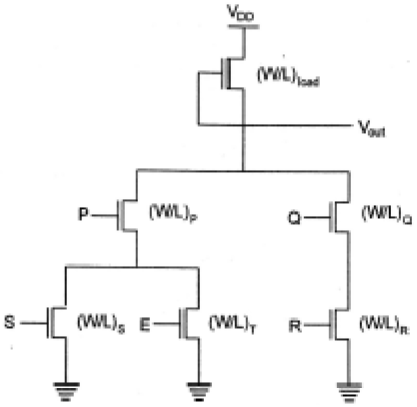

为了实现多个输入变量的复杂功能,为NOR和NAND开发的基本电路结构和设计原理可以扩展到复杂的逻辑门。使用少量晶体管实现复杂逻辑功能的能力是 nMOS 和 CMOS 逻辑电路最有吸引力的特性之一。以以下布尔函数为例。

$$\overline{Z=P\left ( S+T \right )+QR}$$

用于实现该功能的nMOS耗尽负载复合逻辑门如图所示。在此图中,三个驱动晶体管的左侧 nMOS 驱动器支路用于执行逻辑功能 P (S + T),而右侧支路则执行功能 QR。通过并联两个支路,并将负载晶体管放置在输出节点和电源电压V DD之间,我们获得了给定的复函数。每个输入变量仅分配给一个驱动程序。

对电路拓扑的检查给出了下拉网络的简单设计原理 -

- OR 运算由并联驱动器执行。

- AND 运算由串联驱动器执行。

- 反转是由 MOS 电路操作的本质提供的。

如果实现该功能的电路中所有输入变量均为逻辑高电平,则由五个 nMOS 晶体管组成的下拉网络的等效驱动器(W/L)比为

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right ) R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \右)Q}}$$

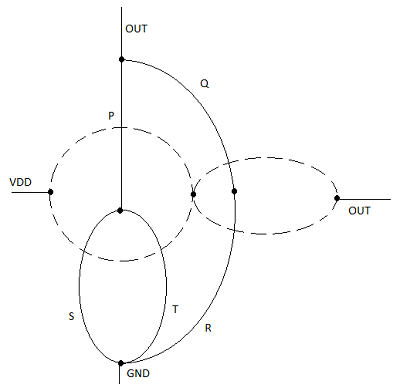

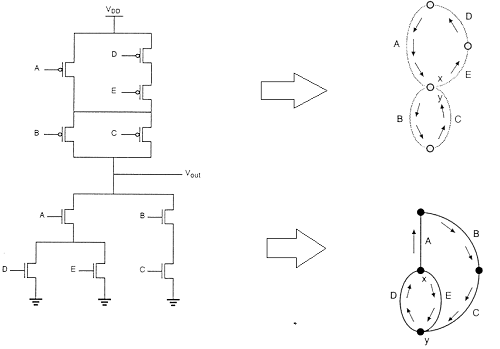

复杂 CMOS 逻辑门

n-net 或下拉网络的实现基于与 nMOS 耗尽负载复杂逻辑门相同的基本设计原理。pMOS 上拉网络必须是 n 网的双网络。

这意味着nMOS网络中的所有并联连接将对应于pMOS网络中的串联连接,并且nMOS网络中的所有串联连接将对应于pMOS网络中的并联连接。该图显示了从 n 网(下拉)图构造对偶 p 网(上拉)图的简单结构。

下拉网络中的每个驱动晶体管由ai 表示,每个节点由下拉图中的一个顶点表示。接下来,在拉图中的每个限制区域内创建一个新顶点,并且相邻顶点通过仅与下拉图中的每条边交叉一次的边连接。这个新图显示了上拉网络。

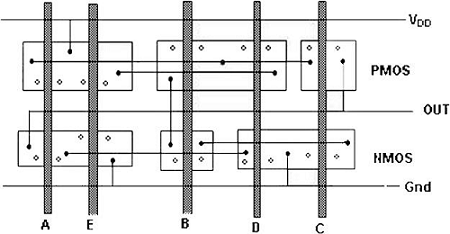

使用欧拉图方法的布局技术

该图显示了复杂功能的 CMOS 实现及其使用任意栅极排序完成的棒图,这为 CMOS 栅极提供了非常非最佳的布局。

在这种情况下,多晶硅柱之间的分离必须允许其间的扩散-扩散分离。这肯定会消耗大量额外的硅面积。

通过使用欧拉路径,我们可以获得最佳布局。欧拉路径被定义为一条不间断的路径,它恰好遍历图的每条边(分支)一次。在下拉树图和上拉树图中查找具有相同输入顺序的欧拉路径。

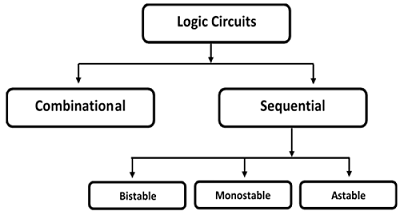

VLSI 设计 - 时序 MOS 逻辑电路

逻辑电路分为两类 - (a) 组合电路和 (b) 时序电路。

在组合电路中,输出仅取决于最新输入的条件。

在时序电路中,输出不仅取决于最新的输入,还取决于较早输入的条件。时序电路包含存储元件。

时序电路分为三种类型 -

双稳态- 双稳态电路有两个稳定的工作点,并且将处于任一状态。示例 - 存储单元、锁存器、触发器和寄存器。

单稳态- 单稳态电路只有一个稳定工作点,即使它们暂时受到相反状态的干扰,它们也会及时返回到其稳定工作点。例如:定时器、脉冲发生器。

Astable - 电路没有稳定的工作点并在几种状态之间振荡。示例 - 环形振荡器。

CMOS逻辑电路

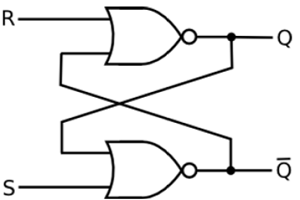

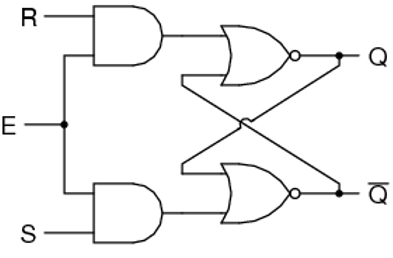

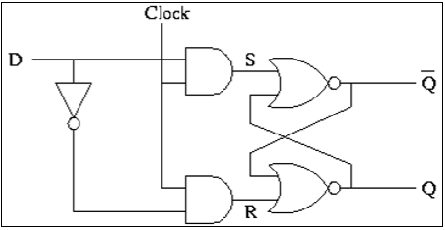

基于或非门的SR锁存器

如果置位输入 (S) 等于逻辑“1”且复位输入等于逻辑“0”。那么输出 Q 将被强制为逻辑“1”。而 $\overline{Q}$ 被强制为逻辑“0”。这意味着 SR 锁存器将被设置,无论其先前的状态如何。

类似地,如果 S 等于“0”且 R 等于“1”,则输出 Q 将被强制为“0”,而 $\overline{Q}$ 将被强制为“1”。这意味着锁存器被重置,无论其先前保持的状态如何。最后,如果输入 S 和 R 都等于逻辑“1”,则两个输出将被迫为逻辑“0”,这与 Q 和 $\overline{Q}$ 的互补性相冲突。

因此,在正常操作期间不允许这种输入组合。表中给出了基于 NOR 的 SR 锁存器的真值表。

| S | 右 | 问 | $\overline{Q}$ | 手术 |

|---|---|---|---|---|

| 0 | 0 | 问 | $\overline{Q}$ | 抓住 |

| 1 | 0 | 1 | 0 | 放 |

| 0 | 1 | 0 | 1 | 重置 |

| 1 | 1 | 0 | 0 | 不允许 |

基于或非门的CMOS SR锁存器如下图所示。

如果S等于V OH且R等于V OL,则并联的晶体管M1和M2都将导通。节点 $\overline{Q}$ 上的电压将呈现逻辑低电平 V OL = 0。

同时,M3和M4均截止,从而在节点Q处产生逻辑高电压V OH。如果R等于V OH且S等于V OL,则M1和M2截止并且M3和M4打开。

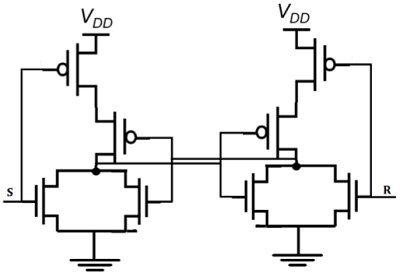

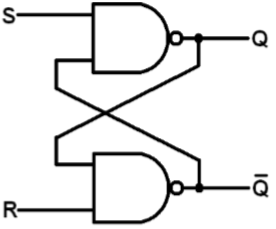

基于与非门的SR锁存器

图中显示了基于 NAND 的 SR 锁存器的框图和门级原理图。S和R输入端的小圆圈代表电路响应低电平有效输入信号。基于 NAND 的 SR 锁存器的真值表如表所示

| S | 右 | 问 | Q′ | |

| 0 | 0 | 数控 | 数控 | 不用找了。锁存器保持当前状态。 |

| 1 | 0 | 1 | 0 | 闩锁设置。 |

| 0 | 1 | 0 | 1 | 锁存复位。 |

| 1 | 1 | 0 | 0 | 无效条件。 |

如果 S 变为 0(同时 R = 1),Q 变为高电平,将 $\overline{Q}$ 拉低,锁存器进入置位状态

S = 0 则 Q = 1(如果 R = 1)

如果 R 变为 0(而 S = 1),Q 变为高电平,将 $\overline{Q}$ 拉低,并且锁存器复位

R = 0则 Q = 1(如果 S = 1)

保持状态要求 S 和 R 都为高电平。如果 S = R = 0,则不允许输出,因为这会导致不确定状态。基于NAND Gate的CMOS SR Latch如图所示。

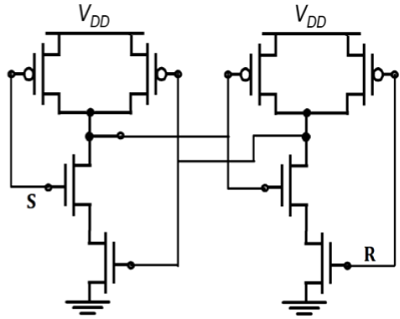

基于与非门的耗尽型nMOS SR Latch如图所示。操作与CMOS NAND SR 锁存器类似。CMOS 电路实现具有低静态功耗和高噪声容限。

CMOS逻辑电路

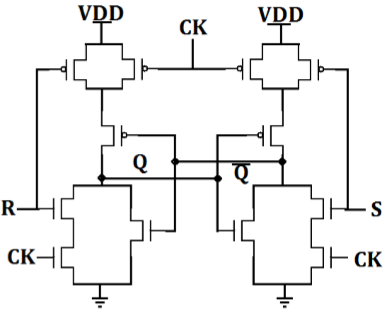

时钟SR锁存器

该图显示了添加了时钟的基于 NOR 的 SR 锁存器。仅当 CLK 为高电平时,锁存器才响应输入 S 和 R。

当 CLK 为低电平时,锁存器保持其当前状态。观察 Q 改变状态 -

- 当 S 在正 CLK 期间变高时。

- 在 CLK 低电平期间 S 和 R 发生变化后,在 CLK 前沿。

- 当 CLK 为高电平时 S 中出现正毛刺

- 当 R 在正 CLK 期间变高时。

图中显示了基于时钟 NOR 的 SR 锁存器的 CMOS AOI 实现。请注意,仅需要 12 个晶体管。

当CLK为低电平时,N树N中的两个串联端子开路,并且树P中的两个并联晶体管导通,从而保留存储单元中的状态。

当时钟为高电平时,电路变成一个简单的基于 NOR 的 CMOS 锁存器,它将响应输入 S 和 R。

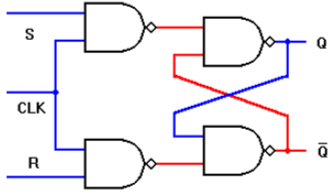

基于 NAND 门的时钟 SR 锁存器

电路由四个与非门实现。如果该电路用 CMOS 实现,则需要 16 个晶体管。

- 仅当 CLK 为高电平时,锁存器才会响应 S 或 R。

- 如果输入信号和 CLK 信号均为高电平有效:即,当 CLK =“1”、S =“1”且 R =“0”时,锁存器输出 Q 将被置位

- 类似地,当 CLK =“1”、S =“0”且

当 CLK 为低电平时,锁存器保持其当前状态。

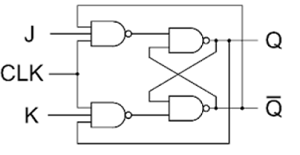

时钟JK锁存器

上图显示了基于 NAND 门的时钟 JK 锁存器。SR锁存器的缺点是当S和R都为高时,其输出状态变得不确定。JK锁存器通过使用从输出到输入的反馈来消除这个问题,使得真值表的所有输入状态都是允许的。如果 J = K = 0,锁存器将保持其当前状态。

如果 J = 1 且 K = 0,则锁存器将在下一个正向时钟边沿设置,即 Q = 1,$\overline{Q}$ = 0

如果 J = 0 且 K = 1,则锁存器将在下一个正向时钟边沿复位,即 Q = 1 且 $\overline{Q}$ = 0。

如果 J = K = 1,锁存器将在下一个正向时钟边沿切换

表中给出的真值表总结了时钟控制 JK 锁存器的操作。

J |

K |

问 |

$\overline{Q}$ | S |

右 |

问 |

$\overline{Q}$ | 手术 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 抓住 |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 重置 |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 放 |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 切换 |

| 1 | 0 | 1 | 0 | 0 | 1 |

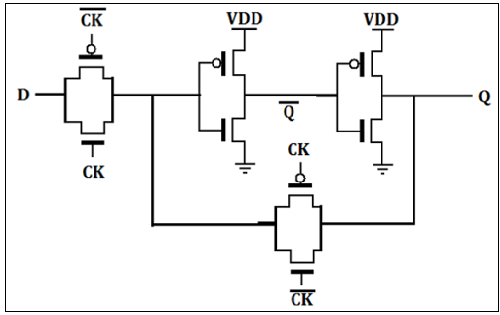

CMOS D 锁存器实现

D 锁存器通常由传输门 (TG) 开关实现,如图所示。输入 TG 由 CLK 激活,而锁存器反馈环路 TG 由 CLK 激活。当 CLK 为高电平时,输入 D 被接受。当 CLK 变低时,输入开路,锁存器设置为先前的数据 D。

VLSI设计-VHDL简介

VHDL 代表超高速集成电路硬件描述语言。它是一种编程语言,用于通过数据流、Behave和结构建模风格对数字系统进行建模。该语言于 1981 年在 VHSIC 计划下首次为国防部 (DoD) 引入。

描述设计

在VHDL中,实体用于描述硬件模块。一个实体可以用以下方式描述:

- 实体声明

- 建筑学

- 配置

- 包裹申报

- 封装体

我们来看看这些是什么?

实体声明

它定义了硬件模块的名称、输入输出信号和模式。

语法-

entity entity_name is Port declaration; end entity_name;

实体声明应以“entity”开头并以“end”关键字结束。方向将为输入、输出或输入输出。

| 在 | 端口可读取 |

| 出去 | 端口可写 |

| 进出 | 端口可读写 |

| 缓冲 | 端口可读写,只能有一个源。 |

架构-

架构可以使用结构、数据流、Behave或混合风格来描述。

语法-

architecture architecture_name of entity_name architecture_declarative_part; begin Statements; end architecture_name;

在这里,我们应该指定我们为其编写架构主体的实体名称。架构语句应位于“begin”和“end”关键字内。架构声明部分可能包含变量、常量或组件声明。

数据流建模

在这种建模风格中,通过实体的数据流是使用并发(并行)信号来表达的。VHDL中的并发语句是WHEN和GENERATE。

除此之外,仅使用运算符(AND、NOT、+、*、sll 等)的赋值也可用于构造代码。

最后,在这种代码中还可以使用一种特殊的赋值,称为 BLOCK。

在并发代码中,可以使用以下内容 -

- 运营商

- WHEN 语句(WHEN/ELSE 或WITH/SELECT/WHEN);

- GENERATE 语句;

- 块语句

Behave建模

在这种建模风格中,实体的Behave作为语句集按指定的顺序顺序执行。只有放在 PROCESS、FUNCTION 或 PROCEDURE 内的语句才是顺序的。

PROCESSES、FUNCTION 和 PROCEDURES 是唯一按顺序执行的代码部分。

然而,作为一个整体,这些块中的任何一个仍然与放置在其外部的任何其他语句并发。

Behave代码的一个重要方面是它不限于顺序逻辑。事实上,有了它,我们可以构建时序电路以及组合电路。

Behave语句有 IF、WAIT、CASE 和 LOOP。变量也受到限制,它们应该仅在顺序代码中使用。VARIABLE 永远不可能是全局的,因此它的值不能直接传递出去。

结构建模

在此建模中,实体被描述为一组互连的组件。组件实例化语句是并发语句。因此,这些语句的顺序并不重要。建模的结构风格仅描述组件的互连(视为黑匣子),而不暗示组件本身或它们共同表示的实体的任何Behave。

在结构建模中,架构主体由两部分组成 - 声明部分(在关键字 begin 之前)和语句部分(在关键字 begin 之后)。

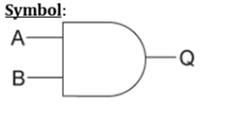

逻辑运算——与门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity and1 is port(x,y:in bit ; z:out bit); end and1; architecture virat of and1 is begin z<=x and y; end virat;

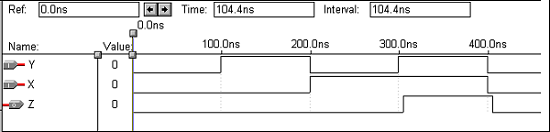

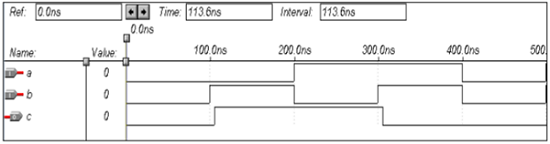

波形

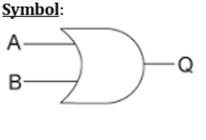

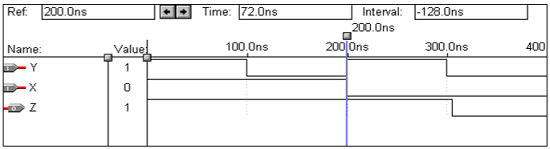

逻辑运算——或门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity or1 is port(x,y:in bit ; z:out bit); end or1; architecture virat of or1 is begin z<=x or y; end virat;

波形

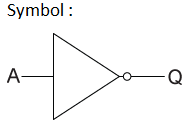

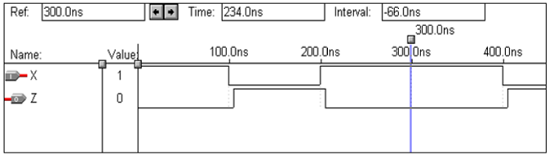

逻辑运算——非门

| X | 是 |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity not1 is port(x:in bit ; y:out bit); end not1; architecture virat of not1 is begin y<=not x; end virat;

波形

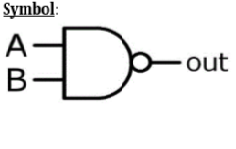

逻辑运算——与非门

| X | 是 | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nand1 is port(a,b:in bit ; c:out bit); end nand1; architecture virat of nand1 is begin c<=a nand b; end virat;

波形

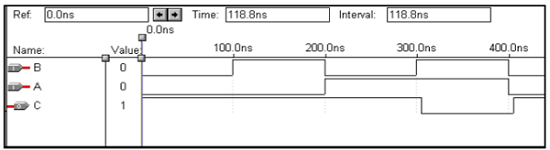

逻辑运算——或非门

| X | 是 | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nor1 is port(a,b:in bit ; c:out bit); end nor1; architecture virat of nor1 is begin c<=a nor b; end virat;

波形

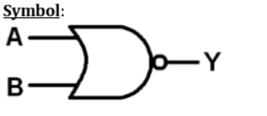

逻辑运算 – 异或门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xor1 is port(a,b:in bit ; c:out bit); end xor1; architecture virat of xor1 is begin c<=a xor b; end virat;

波形

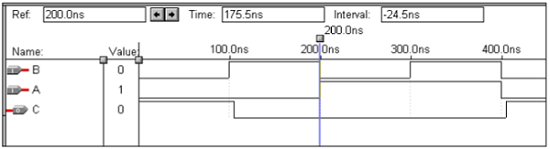

逻辑运算——异或非门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xnor1 is port(a,b:in bit ; c:out bit); end xnor1; architecture virat of xnor1 is begin c<=not(a xor b); end virat;

波形

VHDL编程组合电路

本章介绍组合电路的 VHDL 编程。

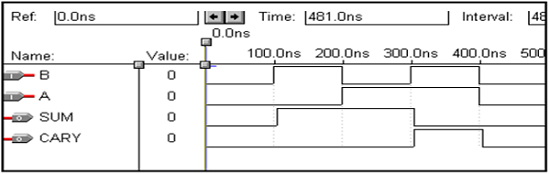

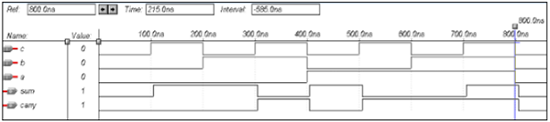

半加器的 VHDL 代码

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity half_adder is port(a,b:in bit; sum,carry:out bit); end half_adder; architecture data of half_adder is begin sum<= a xor b; carry <= a and b; end data;

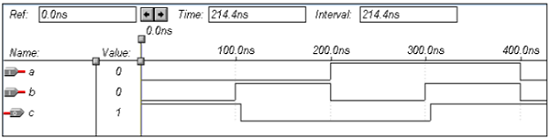

波形

全加器的 VHDL 代码

Library ieee; use ieee.std_logic_1164.all; entity full_adder is port(a,b,c:in bit; sum,carry:out bit); end full_adder; architecture data of full_adder is begin sum<= a xor b xor c; carry <= ((a and b) or (b and c) or (a and c)); end data;

波形

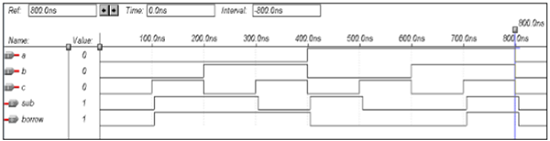

半减法器的 VHDL 代码

Library ieee; use ieee.std_logic_1164.all; entity half_sub is port(a,c:in bit; d,b:out bit); end half_sub; architecture data of half_sub is begin d<= a xor c; b<= (a and (not c)); end data;

波形

全减法器的 VHDL 代码

Library ieee; use ieee.std_logic_1164.all; entity full_sub is port(a,b,c:in bit; sub,borrow:out bit); end full_sub; architecture data of full_sub is begin sub<= a xor b xor c; borrow <= ((b xor c) and (not a)) or (b and c); end data;

波形

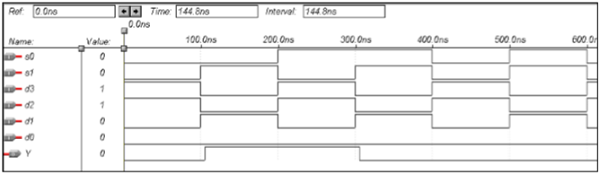

多路复用器的 VHDL 代码

Library ieee;

use ieee.std_logic_1164.all;

entity mux is

port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit);

end mux;

architecture data of mux is

begin

Y<= (not S0 and not S1 and D0) or

(S0 and not S1 and D1) or

(not S0 and S1 and D2) or

(S0 and S1 and D3);

end data;

波形

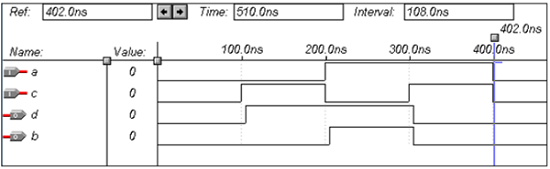

解复用器的 VHDL 代码

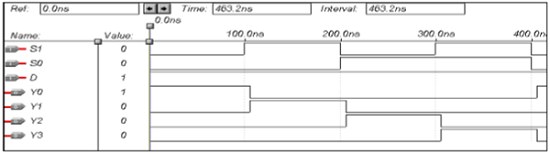

Library ieee; use ieee.std_logic_1164.all; entity demux is port(S1,S0,D:in bit; Y0,Y1,Y2,Y3:out bit); end demux; architecture data of demux is begin Y0<= ((Not S0) and (Not S1) and D); Y1<= ((Not S0) and S1 and D); Y2<= (S0 and (Not S1) and D); Y3<= (S0 and S1 and D); end data;

波形

8 x 3 编码器的 VHDL 代码

library ieee; use ieee.std_logic_1164.all; entity enc is port(i0,i1,i2,i3,i4,i5,i6,i7:in bit; o0,o1,o2: out bit); end enc; architecture vcgandhi of enc is begin o0<=i4 or i5 or i6 or i7; o1<=i2 or i3 or i6 or i7; o2<=i1 or i3 or i5 or i7; end vcgandhi;

波形

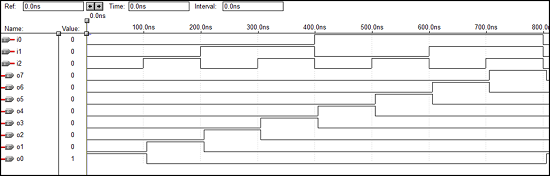

3 x 8 解码器的 VHDL 代码

library ieee; use ieee.std_logic_1164.all; entity dec is port(i0,i1,i2:in bit; o0,o1,o2,o3,o