- VLSI Design Tutorial

- VLSI Design - Home

- VLSI Design - Digital System

- VLSI Design - FPGA Technology

- VLSI Design - MOS Transistor

- VLSI Design - MOS Inverter

- Combinational MOS Logic Circuits

- Sequential MOS Logic Circuits

- VHDL Programming

- VHDL - Introduction

- VHDL - Combinational Circuits

- VHDL - Sequential Circuits

- VLSI Design Useful Resources

- VLSI Design - Quick Guide

- VLSI Design - Useful Resources

- VLSI Design - Discussion

VLSI设计-VHDL简介

VHDL 代表超高速集成电路硬件描述语言。它是一种编程语言,用于通过数据流、Behave和结构建模风格对数字系统进行建模。该语言于 1981 年在 VHSIC 计划下首次为国防部 (DoD) 引入。

描述设计

在VHDL中,实体用于描述硬件模块。一个实体可以用以下方式描述:

- 实体声明

- 建筑学

- 配置

- 包裹申报

- 封装体

我们来看看这些是什么?

实体声明

它定义了硬件模块的名称、输入输出信号和模式。

语法-

entity entity_name is Port declaration; end entity_name;

实体声明应以“entity”开头并以“end”关键字结束。方向将为输入、输出或输入输出。

| 在 | 端口可读取 |

| 出去 | 端口可写 |

| 进出 | 端口可读写 |

| 缓冲 | 端口可读写,只能有一个源。 |

架构-

架构可以使用结构、数据流、Behave或混合风格来描述。

语法-

architecture architecture_name of entity_name architecture_declarative_part; begin Statements; end architecture_name;

在这里,我们应该指定我们为其编写架构主体的实体名称。架构语句应位于“begin”和“end”关键字内。架构声明部分可能包含变量、常量或组件声明。

数据流建模

在这种建模风格中,通过实体的数据流是使用并发(并行)信号来表达的。VHDL中的并发语句是WHEN和GENERATE。

除此之外,仅使用运算符(AND、NOT、+、*、sll 等)的赋值也可用于构造代码。

最后,在这种代码中还可以使用一种特殊的赋值,称为 BLOCK。

在并发代码中,可以使用以下内容 -

- 运营商

- WHEN 语句(WHEN/ELSE 或WITH/SELECT/WHEN);

- GENERATE 语句;

- 块语句

Behave建模

在这种建模风格中,实体的Behave作为语句集按指定的顺序顺序执行。只有放在 PROCESS、FUNCTION 或 PROCEDURE 内的语句才是顺序的。

PROCESSES、FUNCTION 和 PROCEDURES 是唯一按顺序执行的代码部分。

然而,作为一个整体,这些块中的任何一个仍然与放置在其外部的任何其他语句并发。

Behave代码的一个重要方面是它不限于顺序逻辑。事实上,有了它,我们可以构建时序电路以及组合电路。

Behave语句有 IF、WAIT、CASE 和 LOOP。变量也受到限制,它们应该仅在顺序代码中使用。VARIABLE 永远不可能是全局的,因此它的值不能直接传递出去。

结构建模

在此建模中,实体被描述为一组互连的组件。组件实例化语句是并发语句。因此,这些语句的顺序并不重要。建模的结构风格仅描述组件的互连(视为黑匣子),而不暗示组件本身或它们共同表示的实体的任何Behave。

在结构建模中,架构主体由两部分组成 - 声明部分(在关键字 begin 之前)和语句部分(在关键字 begin 之后)。

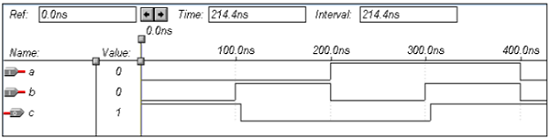

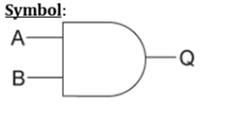

逻辑运算——与门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity and1 is port(x,y:in bit ; z:out bit); end and1; architecture virat of and1 is begin z<=x and y; end virat;

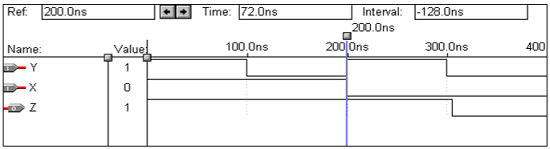

波形

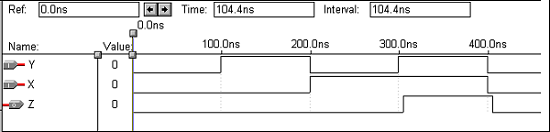

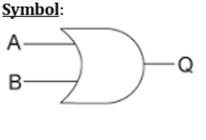

逻辑运算——或门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity or1 is port(x,y:in bit ; z:out bit); end or1; architecture virat of or1 is begin z<=x or y; end virat;

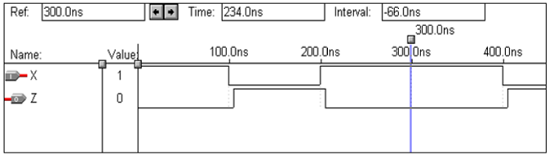

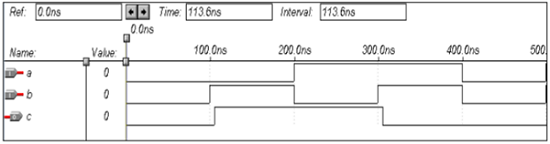

波形

逻辑运算——非门

| X | 是 |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity not1 is port(x:in bit ; y:out bit); end not1; architecture virat of not1 is begin y<=not x; end virat;

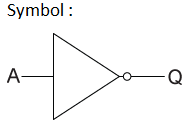

波形

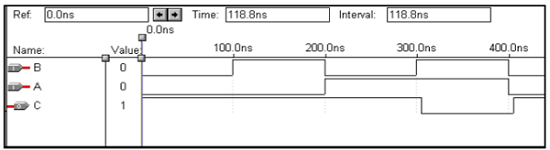

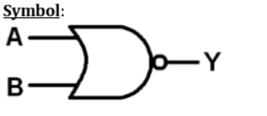

逻辑运算——与非门

| X | 是 | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nand1 is port(a,b:in bit ; c:out bit); end nand1; architecture virat of nand1 is begin c<=a nand b; end virat;

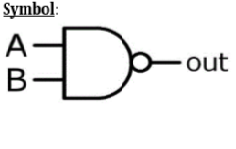

波形

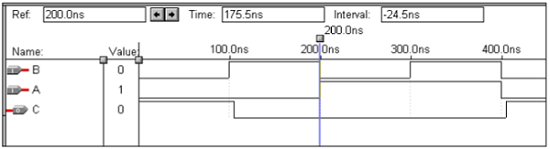

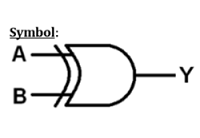

逻辑运算——或非门

| X | 是 | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nor1 is port(a,b:in bit ; c:out bit); end nor1; architecture virat of nor1 is begin c<=a nor b; end virat;

波形

逻辑运算 – 异或门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xor1 is port(a,b:in bit ; c:out bit); end xor1; architecture virat of xor1 is begin c<=a xor b; end virat;

波形

逻辑运算——异或非门

| X | 是 | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xnor1 is port(a,b:in bit ; c:out bit); end xnor1; architecture virat of xnor1 is begin c<=not(a xor b); end virat;

波形